neoVAMS

About neoVAMS

neoVAMS is a high performance multi-partition analog solver extension/plug-in for industry standard SystemVerilog simulators. Simulation speedup is typically 20x-100x depending on design. Uses include:

- Enabling a low cost mixed-signal simulation/verification solution supporting Verilog-AMS and functional models

- Accelerating high cost high end simulation platforms used for large complex modules and SoCs incorporating Spice and AICMs

- Promoting re-use of module-level Verilog-AMS models at SoC level

Benefits include:

- Higher verification coverage as a result of increased testing

- Lower costs associated with model development and maintenance - fewer sets of models needed

- Lower costs associated with test development - less wait time in modify-simulate-debug cycle

- Faster late-stage detailed design-change validation - anything neoVAMS in a DUT will simulate super fast

Features

- High speed Verilog-AMS plug-in for SystemVerilog simulators

- Fast multi-instance analog solver supporting circuit partitioning, resulting in high simulation speed compared to conventional AMS solvers

- Solver boost (up to 2x) for circuits exhibiting a reasonable level of repetition (eg SMPS)

- Support for auto-inserted supply-sensitive Connect Modules when used with Cadence® Xcelium/Spectre

- Built-in Discrete Electrical Multi-Channel Analog Wires for use with functional analog models

- Real-time GUI-based profiler for identifying and fixing simulation-speed bottlenecks

- Compatible with Cadence® Xcelium, Modelsim/Questa-Intel® FPGA, Icarus Verilog; untested with Synopsys® VCS

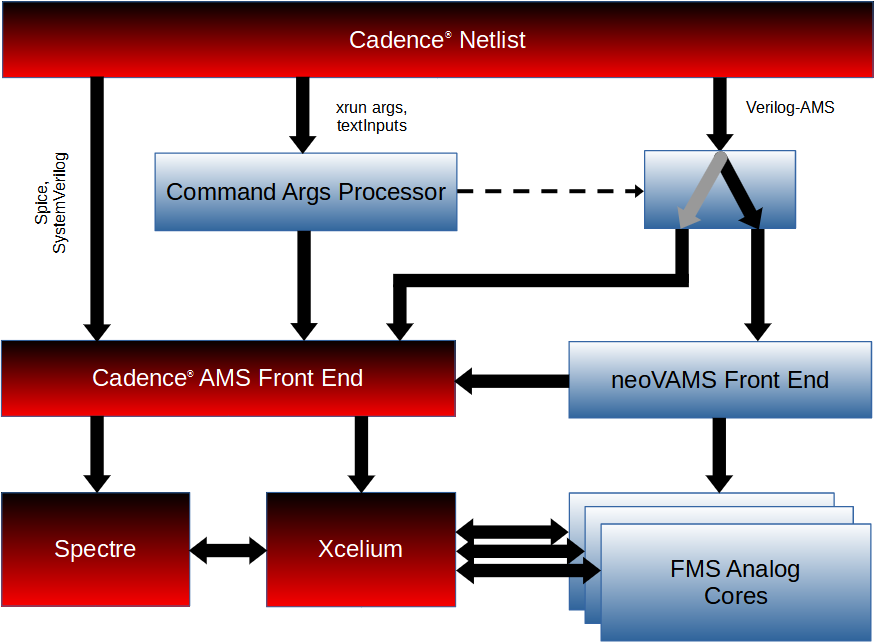

Tool Flow for Complex Design Configurations

neoVAMS integrates neatly with Cadence® Xcelium/Spectre when design configurations include Spice-based views and require support for AICMs. The tool flow requires one simple additional step between "netlist" and "run":

- Netlist the design

- Auto-distribute Verilog-AMS cellviews between Spectre/Xcelium and neoVAMS as desired, and compile/add the neoVAMS cellviews

- Run the simulation

Get Started

- Try online with online-VAMS.

- upload your own design files, or

- try some examples, including a 12-phase PCMC SMPS design running in PWM mode at 2ms/minute.

- Free 3-week evaluations - Contact Us.

- Australian University? Significant discounts.